- 技术(专利)类型 发明专利

- 申请号/专利号 201610624812.2

- 技术(专利)名称 一种三维功率VDMOS器件及其集成方法

- 项目单位

- 发明人 林洁馨 傅兴华 马奎 杨发顺

- 行业类别 人类生活必需品

- 技术成熟度 详情咨询

- 交易价格 ¥面议

- 联系人 李先生

- 发布时间 2021-03-10

北京

北京

客服热线:010-83278899

微信公众号 扫一扫 关注我们

微信公众号 扫一扫 关注我们

项目简介

本发明公开了一种三维功率VDMOS器件及其集成方法,它包括功率单元和芯片层,所述芯片层有二个以上,每个芯片层上均匀分布有二个以上的功率单元,每个功率单元外围设置有独立的终端,每个功率单元外围设置有层间导电互连的TSV通孔,各个芯片层堆叠在一起形成三维功率VDMOS器件;解决了VDMOS器件采用平面集成工艺存在的器件面积随着电流容量增大而增大,严重影响功率系统的集成度,同时信号延迟时间及互连线功耗比重也将越来越大等技术问题。

说明书

技术领域

本发明属于VDMOS器件集成技术,尤其涉及一种三维功率VDMOS器件及其集成方法。

背景技术

功率VDMOS器件作为电力电子设备中的主要元件之一,主要是用来实现电能的变换。是八十年代迅速发展起来的新型功率器件,它比双极型功率器件具有许多优良性能:高输入阻抗、低驱动电流、高速高频、负的电流温度系数、没有二次击穿等。而且VDMOS的漏极从背面引出,集成度更高于功率LDMOS,广泛地应用于各种高速开关电路、开关电源、高功率放大电路、射频功放电路、电力转换电路、电机变频调速、电机驱动、控制电路与功率负载之间的接口电路等。目前,功率VDMOS器件的制作工艺还是沿用传统的平面集成工艺,器件有源层只存在于芯片表面几十微米内,这会导致器件面积随着电流容量增大而增大,严重影响功率系统的集成度,同时信号延迟时间及互连线功耗比重也将越来越大。随着晶体管特征尺寸的缩小,自上世纪60年代起推动信息技术革命的原则——摩尔定律正走向终结。

发明内容

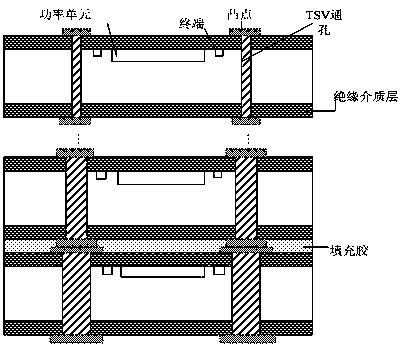

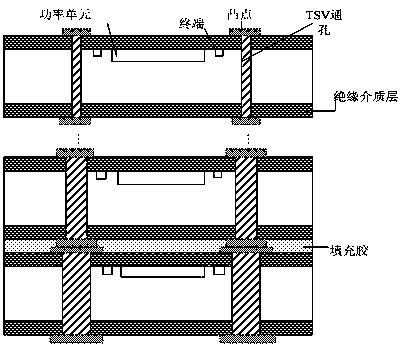

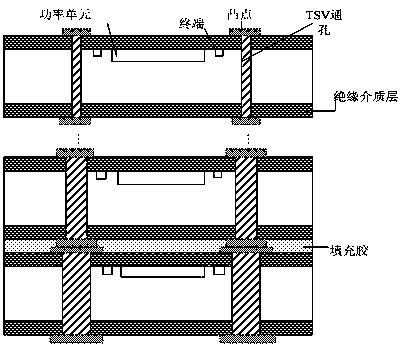

本发明要解决的技术问题:提供一种三维功率VDMOS器件及其集成方法,以解决现有技术的VDMOS器件采用平面集成工艺存在的器件面积随着电流容量增大而增大,严重影响功率系统的集成度,同时信号延迟时间及互连线功耗比重也将越来越大等技术问题。本发明技术方案:一种三维功率VDMOS器件,它包括功率单元和芯片层,所述芯片层有二个以上,每个芯片层上均匀分布有二个以上的功率单元,每个功率单元外围设置有独立的终端,每个功率单元外围设置有层间导电互连的TSV通孔,各个芯片层堆叠在一起形成三维功率VDMOS器件。所述功率单元外围设置有散热的TSV通孔。每个芯片层之间有绝缘介质层,所述绝缘介质层为二氧化硅。各个芯片层间的空隙处有填充胶。所述的各个功率单元外围都设置有独立的终端,所述终端为场限环结构。TSV通孔上方设有凸点。所述三维功率VDMOS器件采用双层金属布线结构。一种三维功率VDMOS器件的集成方法,它包括:步骤1、将VDMOS器件的有源区制作在二个以上的芯片层上,每一芯片层上的元胞平均分成二个以上的功率单元;步骤2、金属布线:将VDMOS器件采用双层金属布线,第一层金属布线将每个功率单元中元胞间的源极连接,将功率单元的栅极引出,第二层金属布线将功率单元间的源极和栅极连接;步骤3、芯片层表面平坦化处理:在完成金属布线后的芯片层上淀积钝化层,然后采用物理化学抛光工艺将芯片层表面平坦化处理;步骤4、刻蚀TSV通孔:在芯片层的功率单元预留处刻蚀出二个以上的TSV通孔,TSV通孔的直径按照芯片层从上至下的顺序逐渐增大;步骤5、TSV通孔填满:采用低温CVD工艺在TSV通孔中淀积绝缘介质层,深槽溅射生长阻挡层及种子层,然后电镀Cu将TSV通孔填满;步骤6、芯片层表面铜抛光:采用物理化学抛光工艺将电镀在芯片层表面的铜抛掉,并将芯片层表面平坦化;步骤7、芯片层正表面氧化:采用低温CVD工艺在平坦化处理后的芯片层正表面上淀积氧化层;步骤8、芯片层背面氧化:对芯片层的背面进行减薄及抛光将TSV通孔底部露出,并用低温CVD工艺在芯片层背面淀积氧化层;步骤9、芯片层正面TSV通孔上方及栅、源极金属上方的氧化层刻蚀接触孔:将芯片层正表面TSV上方的氧化层及用于层间栅极和源极互连的TSV通孔周围的金属上方的氧化层刻蚀出接触孔;步骤10、TSV通孔电镀金:溅射生长阻挡层及种子层,并匀胶保护不需要金属互连的地方,然后电镀金将TSV通孔上方接触孔填满、将层间栅极和源极互连的TSV通孔与周围栅极及源极金属连接,最后去胶并腐蚀掉生长阻挡层及种子层,同时形成芯片正表面键合的凸点;步骤11、芯片层背面TSV通孔及周围漏极上方刻蚀出接触孔:将芯片层背面TSV上方的氧化层及用于层间漏极互连的TSV通孔周围的漏极上方的氧化层刻蚀出接触孔;步骤12、将芯片层背面TSV通孔与芯片层背面漏极互连:溅射生长阻挡层及种子层,并匀胶保护不需要金属互连的地方,然后电镀金将TSV通孔与漏极互连,同时形成键合的凸点,最后去胶,腐蚀掉阻挡层及种子层;步骤13、用胶保护刻蚀栅极和源极的压焊点;步骤14、将芯片层堆叠起来形成三维VDMOS器件。步骤14所述将芯片层堆叠起来形成三维VDMOS器件,堆叠采用的方法为低温共晶键合技术。所述的低温CVD工艺其温度在400°C以下,所述绝缘介质层为二氧化硅,所述生长阻挡层为Ti、Ta或TiN;所述种子层为铜。本发明有益效果:半导体行业路线图将遵循“超越摩尔定律”的战略,而本发明的三维集成技术将是“超越摩尔定律”应用的最好方法。三维集成是一种系统级的架构,它将多层平面芯片堆叠起来,然后通过键合引线或硅通孔(Through Silicon Via,TSV)来实现各层之间的互连,基于TSV的三维集成技术通过缩短全局互连长度,更大程度地改善信号传输速度和功耗特性。本发明基于TSV的三维集成技术应用于功率VDMOS器件,更大程度地缩短全局互连线长度,缩短信号延迟时间;降低了功耗比重,同时将基于TSV的三维集成技术应用于包含功率VDMOS器件的功率系统,可利用三维集成的异质集成技术解决高、低压兼容问题;由于功率VDMOS器件的工作电流越大,构成的元胞数量越多,故把VDMOS器件的有效器件层分割在多个平面层,然后在垂直方向上将它们堆叠起来,并用TSV通孔实现垂直互连,解决了现有VDMOS器件电流容量越大导致器件面积越大问题。又由于功率VDMOS器件在为负载提供尽可能大的输出功率的同时,自身也消耗了很大的电能,消耗的电能将转变为热量使器件的管芯发热,导致有源区温度上升,故作为互连的TSV通孔也充当散热通道;解决了器件发热问题。本发明解决了现有技术的VDMOS器件采用平面集成工艺存在的器件面积随着电流容量增大而增大,严重影响功率系统的集成度,同时信号延迟时间及互连线功耗比重也将越来越大等技术问题。附图说明:图1为本发明三维功率VDMOS器件结构示意图。具体实施方式:一种三维功率VDMOS器件,它包括功率单元和芯片层,所述芯片层有二个以上,每个芯片层上均匀分布有二个以上的功率单元,每个功率单元外围设置有独立的终端,每个功率单元外围设置有层间导电互连的TSV通孔,各个芯片层堆叠在一起形成三维功率VDMOS器件。所述功率单元外围设置有散热的TSV通孔。在每个功率单元外围嵌入散热的TSV通孔,其个数与每个功率单元的功率损耗、TSV通孔的深宽比及TSV通孔中绝缘层的厚度相关;由于各芯片层的VDMOS功率单元的漏极电流通过层间导电互连的TSV通孔最后聚集在最底层芯片的漏极压焊点上,因此三维功率VDMOS器件堆叠层从上至下,嵌入在其中的TSV通孔的直径逐渐增大。层间导电互连的TSV通孔个数与其相连的功率单元的漏极电流之和相关。同时层间导电互连的TSV通孔也作为散热孔,作为散热通道在使用。每个芯片层之间有绝缘介质层,所述绝缘介质层为二氧化硅。各个芯片层间的空隙处有填充胶,填充胶主要是增加导热作用,否则芯片层与层之间有缝隙存在空气,影响热量的传导。所述的各个功率单元外围都设置有独立的终端,所述终端为场限环结构,本发明在各个功率单元外围设置独立的终端目的是防止器件被表面击穿。TSV通孔上方设有凸点,设立凸点可以有利于各个芯片层层间堆叠时的键合。所述三维功率VDMOS器件采用双层金属布线结构。第一层金属布线将每个功率单元中各元胞的源极连接,将功率单元的栅极引出,且第一层金属布线不能跨越每个功率单元的终端;第二层金属布线将各功率单元间的源极和栅极连接。本发明采用双层金属布线结构,主要是防止表面击穿电压降低。一种三维功率VDMOS器件的集成方法,它包括:步骤1、将VDMOS器件的有源区制作在二个以上的芯片层上,每一芯片层上的元胞平均分成二个以上的功率单元;步骤2、金属布线:将VDMOS器件采用双层金属布线,第一层金属布线将每个功率单元中元胞间的源极连接,将功率单元的栅极引出,第二层金属布线将功率单元间的源极和栅极连接;步骤3、芯片层表面平坦化处理:在完成金属布线后的芯片层上淀积钝化层,然后采用物理化学抛光工艺将芯片层表面平坦化处理;步骤4、刻蚀TSV通孔:在芯片层的功率单元预留处刻蚀出二个以上的TSV通孔,TSV通孔的直径按照芯片层从上至下的顺序逐渐增大;步骤5、TSV通孔填满:采用低温CVD工艺在TSV通孔中淀积绝缘介质层,深槽溅射生长阻挡层及种子层,然后电镀Cu将TSV通孔填满;步骤6、芯片层表面铜抛光:采用物理化学抛光工艺将电镀在芯片层表面的铜抛掉,并将芯片层表面平坦化;步骤7、芯片层正表面氧化:采用低温CVD工艺在平坦化处理后的芯片层正表面上淀积氧化层;步骤8、芯片层背面氧化:对芯片层的背面进行减薄及抛光将TSV通孔底部露出,并用低温CVD工艺在芯片层背面淀积氧化层;步骤9、芯片层正面TSV通孔上方及栅、源极金属上方的氧化层刻蚀接触孔:将芯片层正表面TSV上方的氧化层及用于层间栅极和源极互连的TSV通孔周围的金属上方的氧化层刻蚀出接触孔;步骤10、TSV通孔电镀金:溅射生长阻挡层及种子层,并匀胶保护不需要金属互连的地方,然后电镀金将TSV通孔上方接触孔填满、将层间栅极和源极互连的TSV通孔与周围栅极及源极金属连接,最后去胶并腐蚀掉生长阻挡层及种子层,同时形成芯片正表面键合的凸点;步骤11、芯片层背面TSV通孔及周围漏极上方刻蚀出接触孔:将芯片层背面TSV上方的氧化层及用于层间漏极互连的TSV通孔周围的漏极上方的氧化层刻蚀出接触孔;步骤12、将芯片层背面TSV通孔与芯片层背面漏极互连:溅射生长阻挡层及种子层,并匀胶保护不需要金属互连的地方,然后电镀金将TSV通孔与漏极互连,同时形成键合的凸点,最后去胶,腐蚀掉阻挡层及种子层;步骤13、用胶保护刻蚀栅极和源极的压焊点;步骤14、将芯片层堆叠起来形成三维VDMOS器件。步骤14所述将芯片层堆叠起来形成三维VDMOS器件,堆叠采用的方法为低温共晶键合技术。所述的低温CVD工艺其温度在400°C以下,所述绝缘介质层为二氧化硅,所述生长阻挡层为Ti、Ta或TiN;所述种子层为铜。

企业营业执照

专利注册证原件

身份证

个体户营业执照

身份证

专利注册证原件

专利代理委托书

转让申请书

转让协议

手续合格通知书

专利证书

专利利登记簿副本

提交