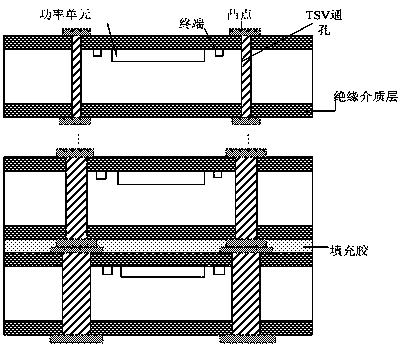

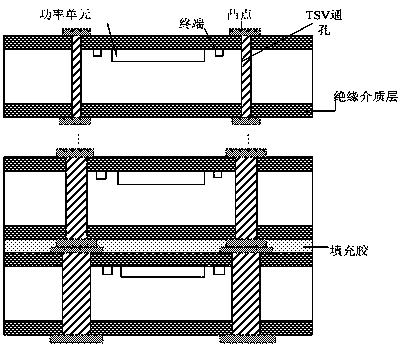

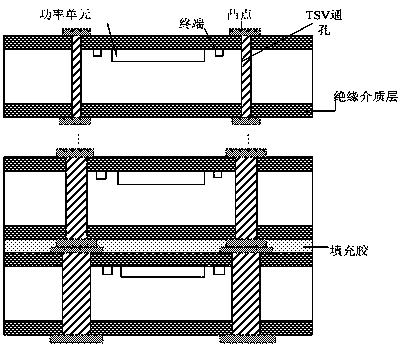

1.一种三维功率VDMOS器件,它包括功率单元和芯片层,其特征在于:所述芯片层有二个以上,每个芯片层上均匀分布有二个以上的功率单元,每个功率单元外围设置有独立的终端,每个功率单元外围设置有层间导电互连的TSV通孔,各个芯片层堆叠在一起形成三维功率VDMOS器件。

2.根据权利要求1所述的一种三维功率VDMOS器件,其特征在于:所述功率单元外围设置有散热的TSV通孔。

3.根据权利要求1所述的一种三维功率VDMOS器件,其特征在于:每个芯片层之间有绝缘介质层,所述绝缘介质层为二氧化硅。

4.根据权利要求1所述的一种三维功率VDMOS器件,其特征在于:各个芯片层间的空隙处有填充胶。

5.根据权利要求1所述的一种三维功率VDMOS器件,其特征在于:所述的各个功率单元外围都设置有独立的终端,所述终端为场限环结构。

6.根据权利要求1所述的一种三维功率VDMOS器件,其特征在于:TSV通孔上方设有凸点。

7.根据权利要求1所述的一种三维功率VDMOS器件,其特征在于:所述三维功率VDMOS器件采用双层金属布线结构。

8.一种三维功率VDMOS器件的集成方法,它包括:步骤1、将VDMOS器件的有源区制作在二个以上的芯片层上,每一芯片层上的元胞平均分成二个以上的功率单元;步骤2、金属布线:将VDMOS器件采用双层金属布线,第一层金属布线将每个功率单元中元胞间的源极连接,将功率单元的栅极引出,第二层金属布线将功率单元间的源极和栅极连接;步骤3、芯片层表面平坦化处理:在完成金属布线后的芯片层上淀积钝化层,然后采用物理化学抛光工艺将芯片层表面平坦化处理;步骤4、刻蚀TSV通孔:在芯片层的功率单元预留处刻蚀出二个以上的TSV通孔,TSV通孔的直径按照芯片层从上至下的顺序逐渐增大;步骤5、TSV通孔填满:采用低温CVD工艺在TSV通孔中淀积绝缘介质层,深槽溅射生长阻挡层及种子层,然后电镀Cu将TSV通孔填满;步骤6、芯片层表面铜抛光:采用物理化学抛光工艺将电镀在芯片层表面的铜抛掉,并将芯片层表面平坦化;步骤7、芯片层正表面氧化:采用低温CVD工艺在平坦化处理后的芯片层正表面上淀积氧化层;步骤8、芯片层背面氧化:对芯片层的背面进行减薄及抛光将TSV通孔底部露出,并用低温CVD工艺在芯片层背面淀积氧化层;步骤9、芯片层正面TSV通孔上方及栅、源极金属上方的氧化层刻蚀接触孔:将芯片层正表面TSV上方的氧化层及用于层间栅极和源极互连的TSV通孔周围的金属上方的氧化层刻蚀出接触孔;步骤10、TSV通孔电镀金:溅射生长阻挡层及种子层,并匀胶保护不需要金属互连的地方,然后电镀金将TSV通孔上方接触孔填满、将层间栅极和源极互连的TSV通孔与周围栅极及源极金属连接,最后去胶并腐蚀掉生长阻挡层及种子层,同时形成芯片正表面键合的凸点;步骤11、芯片层背面TSV通孔及周围漏极上方刻蚀出接触孔:将芯片层背面TSV上方的氧化层及用于层间漏极互连的TSV通孔周围的漏极上方的氧化层刻蚀出接触孔;步骤12、将芯片层背面TSV通孔与芯片层背面漏极互连:溅射生长阻挡层及种子层,并匀胶保护不需要金属互连的地方,然后电镀金将TSV通孔与漏极互连,同时形成键合的凸点,最后去胶,腐蚀掉阻挡层及种子层;步骤13、用胶保护刻蚀栅极和源极的压焊点;步骤14、将芯片层堆叠起来形成三维VDMOS器件。

9.根据权利要求8所述的一种三维功率VDMOS器件的集成方法,其特征在于:步骤14所述将芯片层堆叠起来形成三维VDMOS器件,堆叠采用的方法为低温共晶键合技术。

10.根据权利要求8所述的一种三维功率VDMOS器件的集成方法,其特征在于:所述的低温CVD工艺其温度在400°C以下,所述绝缘介质层为二氧化硅,所述生长阻挡层为Ti、Ta或TiN;所述种子层为铜。

展开

北京

北京

微信公众号 扫一扫 关注我们

微信公众号 扫一扫 关注我们