- 技术(专利)类型 发明专利

- 申请号/专利号 201510644885.3

- 技术(专利)名称 同步补偿型三相马达同步控制电路

- 项目单位

- 发明人 张伟林

- 行业类别 人类生活必需品

- 技术成熟度 详情咨询

- 交易价格 ¥面议

- 联系人 张伟林

- 发布时间 2023-06-27

北京

北京

客服热线:010-83278899

微信公众号 扫一扫 关注我们

微信公众号 扫一扫 关注我们

项目简介

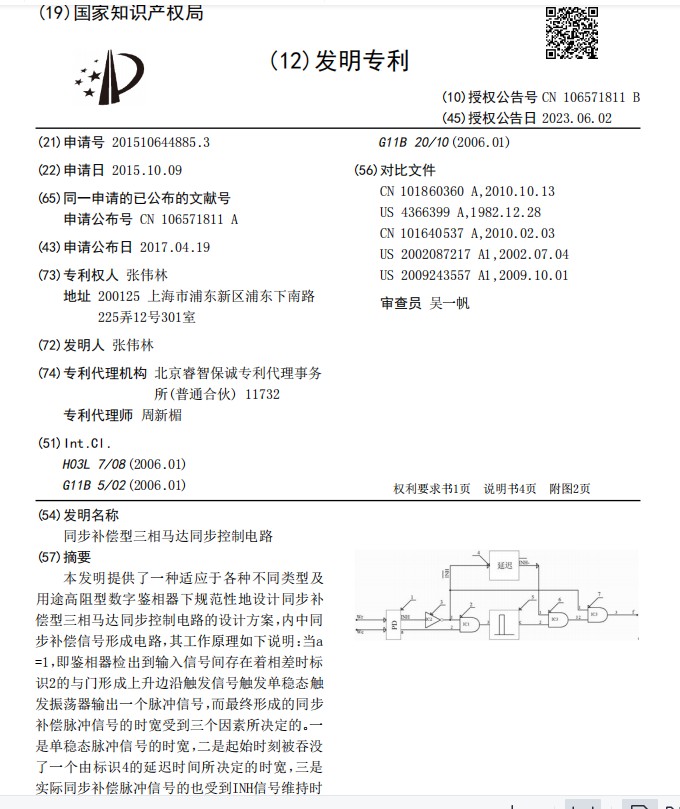

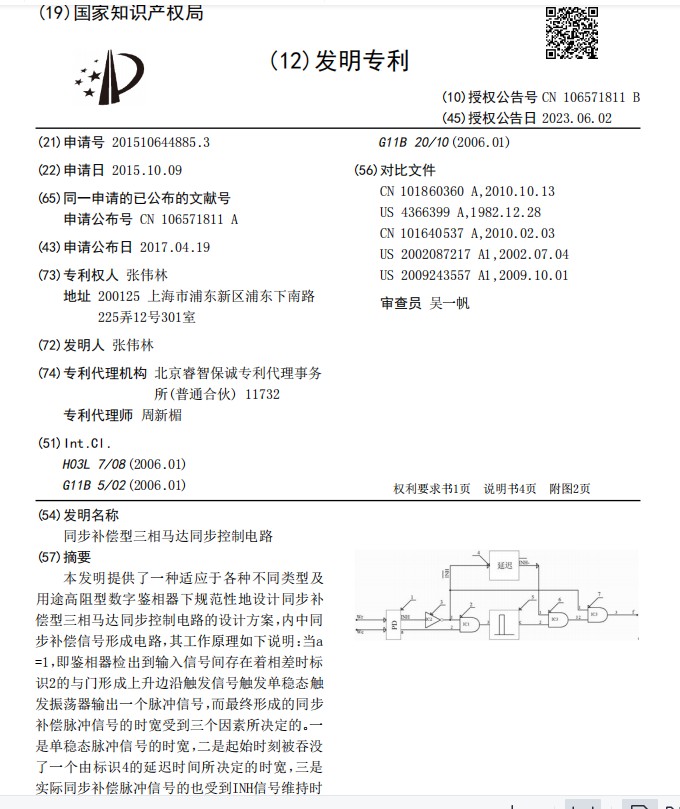

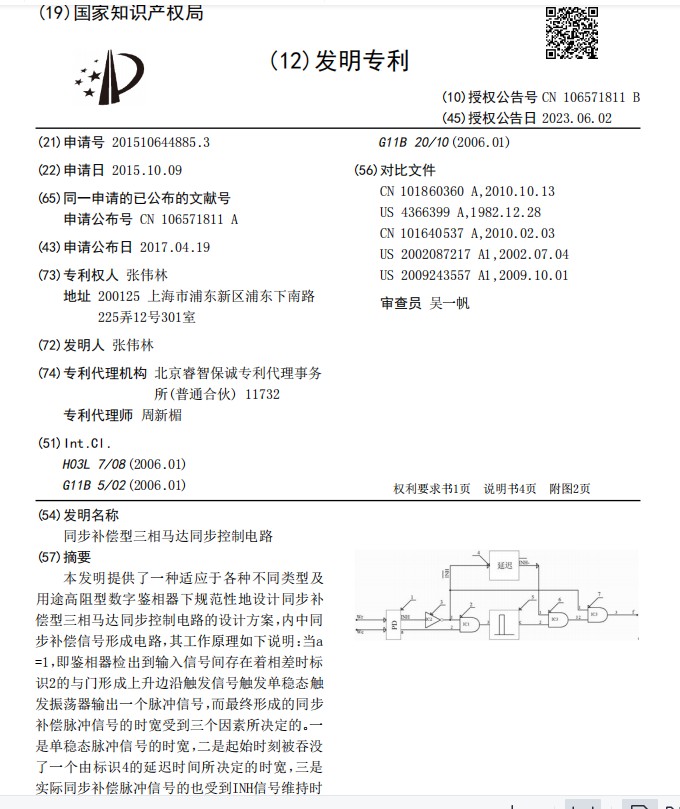

本发明提供了一种适应于各种不同类型及用途高阻型数字鉴相器下规范性地设计同步补偿型三相马达同步控制电路的设计方案,内中同步补偿信号形成电路如图1所示,其工作原理如下说明:当a=1,即鉴相器检出到输入信号间存在着相差时标识2的与门形成上升边沿触发信号触发单稳态触发振荡器输出一个脉冲信号,而最终形成的同步补偿脉冲信号的时宽受到三个因素所决定的。一是单稳态脉冲信号的时宽,二是起始时刻被吞没了一个由标识4的延迟时间所决定的时宽,三是实际同步补偿脉冲信号的也受到INH信号维持时间所限定。

说明书

[0002] 本发明提供了一种规范性设计具有同步补偿功能的三相马达同步控制电路的标准化设计案,本发明所涉及的电路形式不仅适合于通用型数字或模拟IC芯片组建数字鉴相器,更适合应用于集成化电路设计的高阻型数字鉴相器电路中。

[0004] 传统的三相马达同步控制电路,例如CD/DVD再生装置中三相马达伺服电路其构成是由图3所示的振荡,可调分频,鉴相器PD,环路滤波器LF,加法器,驱动三相马达的驱动器,三相马达,初期设定所组成的,并构成三相马达同步控制回路。

[0005]现有三相马达同步控制电路在工作时序中存在着的问题

[0006] 在三相马达伺服电路中容易产生同步不到位现象的产生,其原因是作为锁相环路中一个VCO的马达具有时滞这一特性,一般三相马达转速与直流控制电圧的关系可由下式及图4来表示:

[0007] f(t)=F(v(t))

[0008]这里f是三相马达转速,v是直流控制电圧,t是时间。图4中所存在的问题是对应于直流控制电圧变化的三相马达转速变化所需时间比鉴相器输出信号的周期T长得多,这就是三相马达转速不能跟随直流控制电圧变化的原因所在,例如图4所示曲线中在直流控制电圧变化后的t<T(PD输出周期T)时点上可见,三相马达转速还远没有到达所需转速f1。

[0010] 在图5所示的三相马达同步控制电路一个实施实例方框图中包含了核心技术的图5所示电路,内中:

[0011]a. 同步补偿脉冲原始信号的形成技术;

[0012]b. 同步补偿脉冲信号最大补偿时宽的形成技术;

[0013]c. 供自主同步时宽要求的吞没同步补偿脉冲信号有限时宽的形成技术;

[0014]实际有效同步补偿脉冲信号时宽的形成技术。

[0015] 本发明中所使用的鉴相器是发明名称为《标准化设计高阻型数字鉴相器的结构原理方案》中提供的高阻型数字鉴相器,电路结构方框图为图1所示。本专利申请文件中规定鉴相器中二个输入(端)信号记号为Wr与Wc,输出(端)信号记号为PDo,在三相马达同步控制电路中输入输出信号之间的关系如图2所示。

[0017] 图1是《标准化设计高阻型数字鉴相器的结构原理方案》中规定的鉴相器。对于INH有效型的鉴相器,INH=1时鉴相器输出为高阻态;INH=0时鉴相器输出是进相或者迟相输出,取决于图1中的a的值,如果a=1则进相否则为迟相。

[0018] 图2为本发明中所使用的PD动作状态时序示例图。

[0019]图3为传统三相马达同步控制电路的方框图,图中各个符号及功能说明如下:

[0020]a. 标识1的振荡:由晶振子产生方波,经标识2的可调分频:作分频调整后产生一定基准频率的方波接入到标识3的PD鉴相器的Wr输入端。

[0021]b. 鉴相器的输出经标识4的反相型LF滤波后加入到标识5的加法器“-”端,与加载在加法器“+”端的标识8的初值设定合成后作为VCO控端信号即转速直流控制电圧施加在标识6的驱动器上。

[0022]c. 在驱动器的受控控制下形成标识7的三相马达的转速控制输出,这是由霍尔素子产生三相驱动输出波形,将其合成后作为VCO输出信号反馈到鉴相器的Wc输入端。

[0023] 图4是图3中三相马达同步控制中时滞现象的说明曲线图。

[0024] 图5是本发明所示的三相马达同步控制回路一个实施实例方框图,图中各个符号及功能说明如下:

[0025]1 振荡 高稳定信号源 2 可调分频 数字分频器

[0026]3 鉴相器器PD 例74HC4046 4 LF 有源积分型

[0027]5 加法器 处理直流模拟信号 6 驱动器 三相马达驱动源

[0028]7 三相马达 8 初期设定 直流电平信号

[0029]12 压缩 增益小于1的放大器 13 相位差检出器 EXOR

[0030]14 波形发生器 单稳态触发振荡器 15 高位检出器 直流电平

[0031]16 低位检出器 直流电平 17 SW1 单向开关

[0032]18 SW2 单向开关

[0033] 图6是图5A框内一个具体实例电路方框图,图中各个符号及功能说明如下:

[0034]a. 标识1的PD:高阻型鉴相器,内部有二个控端信号INH与a;

[0035]b. 标识3的反相器:INH信号有效型采用,INH信号有效型改为缓冲器;

[0036]c. 标识2的与门:数字乘法器,当INHa=1时可以形成正跳变脉冲输出信号;

[0037]d. 标识4的延迟:形成INH的延迟一个时间T0的输出INH-,吞没鉴相器输入信号间相差时间一个T0时间,改时间宽度也是锁相环撤除同步补偿脉冲信号后自主可以同步的有效时间宽度;

[0038]e. 标识5的单稳态触发振荡器:形成一个最大时间宽度的同步补偿脉冲信号,如果单稳态触发振荡器形成的脉冲宽度为T1,则同步补偿脉冲信号的最大时间宽度为T1-T0;

[0039]f. 标识6的与门:数字乘法器,形成一个起始时刻被吞没T0时间宽度的单稳态触发脉冲输出,时间宽度为T1-T0;

[0040]g. 标识6的与门:数字开关,控端信号为INH,最终所形成的同步补偿脉冲信号f,如果a=1则有同步补偿脉冲信号;如果以INH检出鉴相器输入信号间相差时刻为基准,则同步补偿脉冲信号在被吞没T0时间宽度后形成一个最大时间宽度为T1-T0,实际终止时刻由INH所决定的实际同步补偿脉冲信号,具体为图7所示。

[0041] 图7是图6中同步补偿信号形成时序图。

[0043]图5所示电路是作为一个通用型的电路方框图,内中A部的工作特征如下:

[0044]a. 基频信号和三相马达输出信号输入到标识13的相位差检出器EXOR即异或门后由其输出d信号触发标识14的波形发生器生成用于同步补偿型信号的单稳态脉冲信号e。

[0045]b. 检出鉴相器高位输出标识15的高位检出器,并由其输出作为控端信号,控制标识17的SW1开关输出窗口宽度受控的波形发生器生成脉冲信号f。

[0046]c. 检出鉴相器低位输出标识16的低位检出器,并由其输出作为控端信号,控制标识18的SW2开关输出窗口宽度受控的波形发生器生成脉冲信号g。

[0047]d. 脉冲信号f为正相直流信号,脉冲信号g为负相直流信号在图3所示的传统三相马达同步控制回路中加法器上合成后成为三相马达的直流同步控制信号。

[0048] 对于一个由时滞型VCO构成的锁相环路,可能存在着补偿的实际要求,而如何补偿有以下五个最佳化补偿准则:

[0049]准则1 补偿信号必须在鉴相器的输出信号出现时点输入到VCO的输入端;

[0050]准则2 补偿信号的最大连续时间和补偿信号的振幅必须不被鉴相器的输出信号所控制;

[0051]准则3 补偿信号的连续时间必须受鉴相器的输出信号所控制;

[0052]准则4 补偿动作结束后补偿信号必须不对PLL环路的动作产生影响;

[0053]准则5 补偿信号的方向性必须与鉴相器的输出信号的方向性一致。

[0054]实际上,此类时滞型VCO在组环时所引出的二个问题需要设计工作者慎重处理并予以克服,其一是“加速度”,其二是“惯性”,这二个问题是相辅相成的孪生问题。“加速度”问题简言之:尽管VCO控制电压已到达“锁定频率”所对应的电平值,但是,VCO的输出频率并未追踪到达“锁定频率”而是在偏离的频率上。其原因是驱动电流无法同步到达所引起的,即一个带有较大“惯性”的VCO,若要达到它的“锁定频率”输出时所需的时间取决于所施加的“加速度”即驱动电流的大小。理论上这一所需时间是趋于无穷大的,现实应用上采用变通实现方式即施加“过度驱动电流”来减小所需的时间。由此,在应用设计上必须面临着另一个相伴而生的孪生问题:由于施加“过度驱动电流”必然存在着一个时间窗口,在这一窗口内的VCO工作频率高于锁定频率,这种基于“惯性”的VCO输出频率也同样地难易调控的。

[0055]一般而言,图5中的低位检出器相应一路可以不需要,同时该结构图是针对现有高阻型鉴相器例如74HC4046类鉴相器的。针对发明名称为《标准化设计高阻型数字鉴相器的结构原理方案》中鉴相器,形成一个本发明核心技术内容的图6所示电路方框图,该电路的工作特征:

[0056] 当a=0,即图2中的Wc属于进相时由于标识2的与门并不会形成上升边沿信号,则标识5的单稳态触发振荡器并不会形成一个脉冲信号输出,所以信号f维持在一个GND电位不变而不会形成同步补偿脉冲信号。但是当a=1,即图2中的Wc属于迟相时,即当鉴相器检出到输入信号间存在着相差时标识2的与门形成上升边沿触发信号触发单稳态触发振荡器输出一个脉冲信号,而最终形成的同步补偿脉冲信号的时宽受到三个因素所决定的。一是单稳态脉冲信号的时宽,二是起始时刻被吞没了一个由标识4的延迟时间所决定的时宽,三是实际同步补偿脉冲信号的也受到INH信号维持时间所限定。

[0057] 最终,将上述的同步补偿脉冲信号f叠加到图5中标识5的加法器内,完成了二个设计目标:形成一个补偿脉冲信号时宽受控,即比例等化于实际补偿需求数量的脉冲,与留有一定时间宽度供自主同步的锁相环路工作要求。

[0058] 设计时,标识5的单稳态触发振荡器所产生的脉冲时宽及驱动时的限幅电路作用不能造成过于“加速度”而难易曳引锁相环进入同步状态;标识4的延迟作用的时宽应有足够的长度确保锁相环路自主地进入同步状态。

[0059]综合以上内容,基于发明名称为《标准化设计高阻型数字鉴相器的结构原理方案》中鉴相器,可以实现同步补偿型三相马达同步控制这一实际要求的电路。

[0060]备注:

[0061]发明专利申请中的《标准化设计高阻型数字鉴相器的结构原理方案》是本发明专利申请的发明人与申请人为同一人,在同一申请日提交的一组发明专利申请文件。

企业营业执照

专利注册证原件

身份证

个体户营业执照

身份证

专利注册证原件

专利代理委托书

转让申请书

转让协议

手续合格通知书

专利证书

专利利登记簿副本

提交